AMD’s Ryzen 9000 series of processors is pretty good, isn’t it? Well, imagine a 50 percent increase in processor cores, higher clock frequencies, a bucket load more cache and revamped IOD – and you’ve a general idea of what team red are planning for Zen 6; at least according to the rumors.

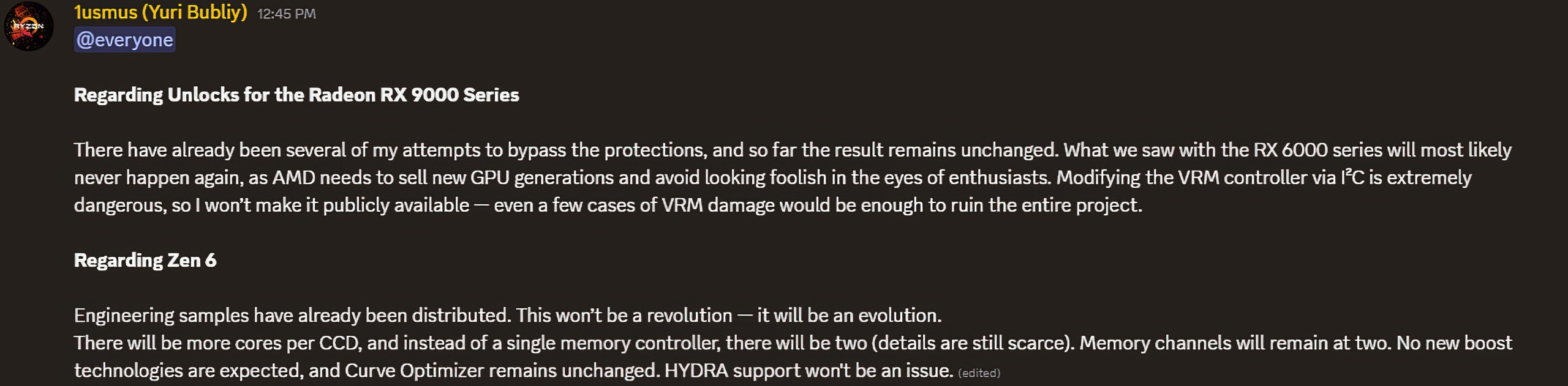

New rumors have popped up from Yuri Bubily, the create of Hydra Tuning Software (Yuri perhaps is better known as 1usmus) and provided several titbits of what we can expect from the next-generation of Zen 6 powered Ryzen CPUs (which I’ll call Ryzen 10000 for this article).

According to 1usmus, Engineering Samples of Zen 6 have been distributed to key partners and the architecture isn’t a revolution, but instead an evolution.

“There are more cores per CCD” says Yuri, which lends further credibility of 12 core CCDs from myself and several others online. This will be for the ‘classic’ CCD configuration, though the dense variant increases core counts to at least 16 (again, according to rumors).

In theory, this wil bring 24 cores / 48 threads to the highest end Ryzen 10k products for AMD’s desktop line (also known as Olympic Ridge), a 50 percent uptick since AMD moved to 16 cores back in the Ryzen 3950x (powered by Zen 2) way back in 2019.

“Instead of a single memory controller, there will be two (details are still scarce). Memory channels will remain at two. No new boost technologies are expected, and Curve Optimizer remains unchanged. Hydra support won’t be an issue” he adds.

Tackling that in order: the CPUs still appear to be on the AM5 platform, and yes dual channel memory remains in place (so, in theory your current AM5 setup should be good to go). That said, there is a dual IMC design; but as Yuri said – the exact nature of how this works remains a mystery.

From what the general rumors are, AMD want to drastically increase bandwidth and reduce latency between the CCDs. I was told AMD is moving from SERDES to Parallel interface, though of course that is from a source, and I wish to stress it could be wrong.

For safe of transparency, I also reached out to a few folks regarding the dual memory controllers and heard little back. The only thing I was told is that some of the changes for Zen 6 might cause problems for (some) AM5 motherboards; but the exact reason for this isn’t clear.

It’s pretty well understood from rumors at this stage that Zen 6 should handle up to 8000mts memory, which is also the same DDR5 transfer rate Intel’s Nova Lake processors will be shooting for too.

Clock speeds for Zen 6 aren’t confirmed of course. A source told me that 6Ghz plus should be very attainable, with a second source stating that the shift from N4 to N2P (the TSMC node Zen 6 Medusa)

Here’s a tl;dr of some of the points and rumors of Zen 6 so far:

- Ryzen will be 12C per CCD, based on N2P.

- 2x CCD / 24 core / 48 threads total.

- AM5 platform support

- IPC gain estimates are all over the place, but 10%~ seems reasonable

- Zen 6 retains 1MB L2 per core

- Final Clock targets are too early. I’m told that at 1.1v, about 1.15x performance can be had from the shift of N4 to N2P; but AMD might target a vmax reduction. Potentially offset with extra metal layers.

- AMD is moving from SERDES to Parallel interface; assuming this is true it could reduce latency / improve bandwidth.

- 48MB L3 cache per CCD, X3D cache potentially 50 percent larger per stack too.

- Memory support appears to be the same 8000MTs as NVL

- Desktop Medusa launches H2 2026, with mobile Q1 2027

It will be very interesting to see how well AMD’s next generation parts perform – particularly against Nova Lake. The two designs are rather different from each other, with AMD’s 24 cores sporting SMT of course, but Intel’s 16 P cores only single thread only, but augmented with 32 E cores and 4 LP cores too. Panther Cove and Arctic Wolf will be pretty impressive; with the e cores being a chunky improvement in IPC.

The rumor mill also points to Intel embracing 3d vCache (errr, sorry I mean bLLC); with variants of at least 144MB.

Thanks to WCCFTech for the initial discovery of the info